Directory digitális integrált áramkörök

2.5.3. JK-flip-flop

JK-flip-flop vannak osztva univerzális és kombinált. Univerzális JK-flip-flop van két bemeneti adata J és K szerint a J bemeneti flip-flop van beállítva, hogy Q = 1, / Q = 0, és a bejegyzés egy K-state Q = 0, / Q = 1.

JK-flip-flop eltér az RS-ravaszt elsősorban, hogy megszűnt a bizonytalanság merül fel, hogy a RS-ravaszt egy adott kombinációja bemeneti jelek.

Sokoldalú JK flip-flop, hogy végre tudja hajtani a funkció RS, T- és D-ravaszt.

Kombinált JK-flip-flop eltér a jelen lévő további univerzális aszinkron bemenetek S és R a flip-flop Előbeállítással egy bizonyos állapotban (logikai 1 vagy 0).

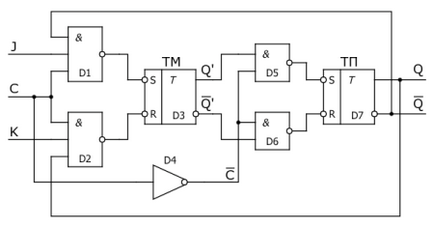

A legegyszerűbb JK flip-flop lehet beszerezni a szinkron RS-kioldó dinamikus ellenőrzés, ha bevezetjük további visszajelzést a kimeneteket a bemenetek a flip-flop, amely megszünteti a bizonytalanságot az állapot táblázatban (ábra. 2.50.a).

Ábra. 2.50.a. Konvertálása szinkron RS flip-flop a JK-flip-flop;

Ha a bemenet J és K alkalmazni logikai-egy szintet, akkor megkapjuk a T-flip-flop, amely kapcsolók az egyes bemeneti impulzus (ábra. 2,50, b).

Ábra. 2.50.b. Conversion JK-flip-flop a T-flip-flop;

Ábra. 2.50.v adott szimbólum JK-flip-flop és az állam táblázatot. Ha a bemeneti jel J = K = 0, a flip-flop nem változik az állapotban, mivel az alacsony szintű feszültség egyik bemenetére AND elem felülbírálja NOR ppohozhdenie jeleit más bemenetei és tartja a kimeneti jel az aktuális logikai állapot.

Ábra. 2.50.v. szimbólum JK flip-flop

Táblázat első JK flip-flop

Ha a bemenet J és K alkalmazni kölcsönösen ellentétes szinteket, amikor a feszültséget, hogy a differenciális bemenet C JK-flip-flop kimenet úgy van beállítva, hogy az ugyanabban az állapotban. Amikor alkalmazni a bemenetek J és K egyidejűleg magas trigger feszültség szinten van kapcsolva, hogy egy állam ellentétes az előzőhöz, ha az óra C bemenet alkalmazni feszültségesés.

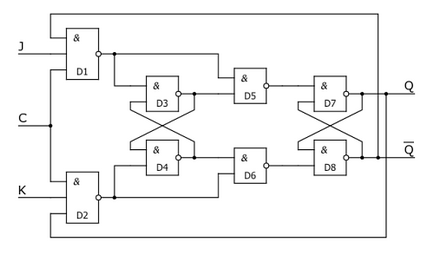

Ellenőrző teljes órajel jut a bemeneti C használják kétfokozatú flip-flop (ábra. 2.50.g).

Ábra. 2.50.g. kétfokozatú JK-flip-flop;

Ez a trigger is van egy visszajelzést kimenet bemenet kivételével határozatlan kiváltó feltétel.

Ábra. 2.50.d. kétfokozatú JK flip-flop az ÉS-kapu NOR

A szimmetrikus vezérlő áramkör beindítja a második szakaszban;

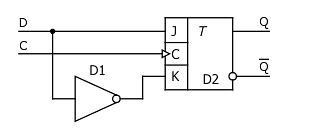

A JK-flip-flop is megkapják a D-flip-flop, ha a K bemenete csatlakozik a bemeneti J keresztül egy további inverter (ábra. 2,50 d).

Ábra. 2.50.e. Conversion áramkör JK-flip-flop a D-flip-flop

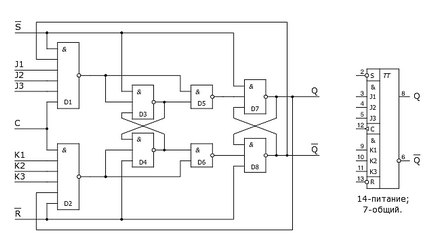

Mikroáramkör TB1 (ábra. 2,51) egy univerzális kétfokozatú JK-flip-flop.

Ábra. 2.51. Kombinált JK flip-flop - a szerkezet a chip, szimbólum és chip pinout TB1.

Eseményindítóján invertált bemenetek AC / S és a reset / R, R. E. aktív alacsony. Ha ezek a bemenetek alkalmazni ellenkező szint (alacsony - 0, és a magas - 1), a bemenetek J, K, és C nem hat, és a feltétel Q kimenet és / Q ravaszt definiált jelek a bemeneteken / S és / R, a állapot táblázatot (Táblázat 2.27. ).

2.27. vezérlő állapota TV1

Ha a bemenet / S és / R benyújtott nagyfeszültségű szinten a flip-flop lehet letölteni információt a J és K bemenetek vagy tárolja (lásd. Az állam a táblázatot). Mind a J és K bemenetek van látva egy kapu 3I, azaz TB1 chip három bemenete J és K három bemenettel C Log inverz dinamikus szinkronizálást. kétlépcsős indítókapcsolót állapotban felfutó és lefutó élek a pozitív impulzus alkalmazott az óra bemeneti C. Információs a J és K bemenetek betöltjük az első szakaszban flip-flop (elemek DD1.3 és DD1.4), amikor a bemeneti feszültség C alacsony és magas (a széle), és átvisszük a második szakaszban flip-flop egy órajel lefutó éle (lefutó él). A bemeneteken J és K nem változnak, ha a bemeneti / C van egy magas szintű feszültséget. Álló Q és / Q kimenetek definiálatlan, ha a bemenetek / S és / R egyidejűleg alkalmazni az alacsony szintű feszültséget, azaz. E. jelek kombinációja / S = / R = 0 tilos.

Mikroáramkörök és TB6 TV9, TV10 és TB11 tartalmaznak két JK-flip-flop egy közös tápvezetékbe (ábra. 2,52).

Ábra. 2.52. Szerkezet, a szimbólumot, és pinout chips TB6, TV9;

Ábra. 2.52a. Szerkezet, szimbólum és a chip pinout TV10;

A órajel bemenete az összes flip-flop inverz dinamikus, így az adatok a bemenet J és K át a kimenetek Q és / Q a negatív differenciál impulzus S. Amikor az impulzus a bemeneti C megy a magas vagy alacsony, a bemeneteken J és K nem kell módosítani . Tájékoztatás a bemenetek J és K be kell tölteni a flip-flop, amikor a C van jelen a bemeneti magas szintű feszültséget.

Ne kiváltó bemeneti áramkör TB6 presetter / S, ezért az állapot táblázatban (kombinált JK-flip-flop) van szükség, hogy megszüntesse az első sor (aszinkron telepítés 1). Ha a bemeneti / R kell táplálni egy alacsony szintű feszültséget, a bemenetek J, K és C nem.

TV10 chipek nincs kiváltja egy nullázó bemenete / R, ezért, az állapot táblázatban kombinált JK-flip-flop ki kell zárni a második sor (aszinkron reteszelhető 0).

A TV10 chipek TB6 és állapot táblázata nincs értelme, és a harmadik sorban, azaz. K, hogy csak egy aszinkron bemenet (vagy / S, A / R). Eseményindítók TV11 chipek eltérően TV9 chip triggerek két közös vezérlő áramkör: az óra bemeneti / C, és az aszinkron reset bemenet / R (ábra 2.53.).

Ábra. 2.53. Szimbólum és pinout TV11 chips

TV14 és TV15 chipek amelyek két kombinált JK-flip-flop váltja pozitív eltérés szinkronizáló impulzus t. E. Közvetlen dinamikus input C. A megkülönböztető jellemzője ezeknek chipek kiváltja, hogy a második adatbeviteli / K - inverz, így nagyon könnyű JK-flip-flop alakítja D-flip-flop (ábra 2.54.).

Ábra. 2.54. TV15 szerkezete, szimbólumok és pinout TV14 és TV15

Állapota kiváltó ingerek a táblázatban foglaljuk össze. 2.28.

Táblázat 2.28. kiváltó állapot TV15