Grafikai tervezés vagy szöveges Verilog

Grafikai tervezés vagy szöveg Verilog / VHDL?

Megkockáztatom, hogy megérintse az ilyen holivarnuyu tárgya: összehasonlítása két módszer kidolgozása, grafikus beviteli rendszer és egy szöveges leírás a projekt HDL Verilog / VHDL nyelven.

Melyik módszer a jobb?

Azt kell mondanom, hogy én vagyok híve a szövegbevitel, így biztosan én veszi nézhet elfogult. Mindazonáltal itt van még egy fontos megjegyzés a témával kapcsolatban:

- projekt lehet jól teljesített, és elgondolkodva nem számít, melyik módszert alkalmazzák, mint ahogy a rossz tervezés lehet tenni a használatát áramkör képviselet a leírást a Verilog / VHDL. Azaz, a projekt minősége inkább függ a képesség a programozó, mint a kiválasztott eszköz (bár a programozó saját preferenciái és egyedi élményt a fejlesztési környezet).

- függetlenül attól, hogy a projekt bemutatásának formájában HDL szövegek vagy az ábrák, a fordító (elméletben) a kívánatos és szükséges, szintetizálni azonos optimális utat a firmware az FPGA. Mindenesetre, a fordító optimalizálja kombinációs logika törli a nem használt elemek, trigger, szintetizálni és optimalizálja kötéslistában.

Most nézzük meg, mindegy előnyeit és hátrányait a módszerek fejlesztése a program vagy szöveges formában.

Hagyományosan, több, egymással összefüggő értékelésének kritériumai digitális projektek kidolgozására eljárás FPGA és ASIC: kényelem, a gyorsaság fejlesztése, a teljesítmény, a hordozhatóság, a kód kezelhetőség és a megbízhatóság.

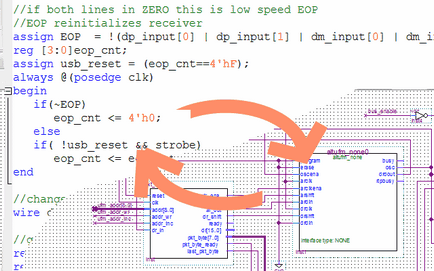

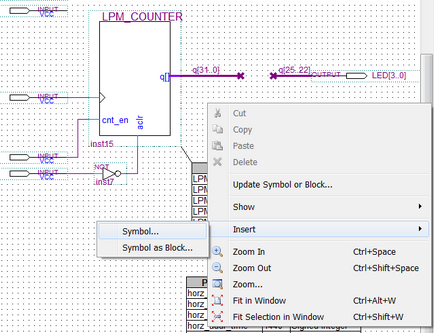

Nos, a Quartus II környezet rajz rendszerek nem jöhet szóba. Ha azt szeretnénk, hogy az új alkatrész, hogy az áramkör, szükséges, hogy végre egy műveletsor, mint a „jobb klikk” => választás a Beszúrás menü => Symbol => később a párbeszédablak kiválasztási listán könyvtári primitív => telepítse azt az áramkört. Aztán néha még mindig a szerkeszteni kívánt tulajdonságait a kiválasztott elem, és ez ismét egy egér, dialógusok, majd, miután sok óra munka az egérrel - a betegség a kezét, „alagút szindróma.”

Hány egér mozgását és hány kattintás kell tennie, hogy egy új elem, hogy a rendszer a Altera Quartus II környezetben?

Természetesen a sebesség fejlődése szorosan összefügg a kényelmet tervezésekor a környezet (lásd első bekezdés).

Általában az emberek, akik festeni rendszer azt mondják, hogy nem törődnek a sebességet, mert gondoltam a projekt sokkal tovább tart, mint a rajz. Valószínűleg ez a helyzet, ez is egyetértenek.

Sőt, magam is gyakran használják a grafikus bemenet. Gyakran a projekt van egy kép fájlt a legfelső szintű hierarchiát. További modulokat tartalmazza a hierarchiában sem Verilogban olyan alkatrészek létrehozott varázsló Altera FIFO típusú vezérlő eleme DDR, SRAM modul vagy PLL, valami más. Egyszerű design és felhívni, de fokozatosan egyre bonyolultabb idővel szerkeszteni egyre nehezebb és nehezebb. Meg kell nyomni a grafikus objektumok, alkatrészek, vezetékek, gumiabroncsok, beszúrni valami újat. Ez a mozgás sémaobjektumok vesz igénybe sok időt, különösen, ha a tervező van értelme a szépség, és ő szereti az áramköri elemekkel Grid. Előfordulhat, hogy a munka helyett a saját projektek ember dolgozik mozgó alkatrészeket. Nyomtatás nagy grafikai tervezés a nyomtató nehezebbé válik, A4-es méret nem megfelelő, akkor kell az A2 és az A1-es, vagy a ragasztó lapok.

Ezenkívül meg kell jegyezni, hogy a sebességet a fejlődés nagymértékben függ az adott programozási nyelv funkciók vagy tervezési környezetben.

És egy fontos pont: minden lehet levonni az áramkör leírható szöveges nyelv HDL, de nem az összes, hogy mi van írva a HDL nyelven könnyen megvalósítható az áramkörben. Íme néhány példa:

modul hvsync (

// bemenetek:

bemeneti huzal pixel_clock,

// kiírja:

kiadási reg hsync,

kiadási reg Vsync

);

// videojel paraméterek alapértelmezett 1440x900 60Hz

paraméter horz_front_porch = 80;

paramétert horz_sync = 152;

paramétert horz_back_porch = 232;

paramétert horz_addr_time = 1440;

paraméter vert_front_porch = 3;

paramétert vert_sync = 6;

paraméter vert_back_porch = 25;

paramétert vert_addr_time = 900;

.

- Egy másik fontos jellemzője a design a szöveg Verilog HDL - ez egy olyan lehetőség feltételes fordítási projektet. Például a projekt kódrészlet Amber (ARM-kompatibilis processzor és a rendszer a chipen).

i_irq (amber_irq),

.i_firq (amber_firq),

o_wb_adr (m_wb_adr [1])

.o_wb_sel (m_wb_sel [1])

.

A projekt lehet beilleszteni, összeállított egy 5-fázisos processzor (ez gyorsabb, de tovább tart, logika) vagy 3-szakaszban processzor (lassabb de kevesebb logika). És ez a feltételes fordítás zajlik, attól függően, hogy az adott környezetben AMBER_A25_CORE. Nem tudja használni a feltételes fordítási a rendszereket. Feltételes összeállítása szükséges, amikor a projekt már számos megvalósítási például a különböző típusú FPGA hasonló projektek szerepelnek a hibakeresés modulprojektet, hogy a végtermék nem tartalmaz, és így tovább.

- A harmadik példa - a különleges szerkezeti Verilog HDL nyelv, amely lehetővé teszi, hogy létrehoz és helyezze a projektben összekapcsolt esetekben más modulokkal. Például itt van egy pillantást a kódot Verilog:

modul inst_loop

(

bemeneti huzal óra,

bemeneti huzal,

kimeneti vezetéket ki

);

genvar index;

generál

az (index = 0; index <4; index=index+1)

kezdődik. fu

huzal o_q;

ha (index == 0)

func # (index) func_inst (

.fclk (nappal),

.d (a),

.q (o_q)

);

más

func # (index) func_inst (

.fclk (nappal),

.d (fu [index-1] .o_q),

.q (o_q)

);

vég

endgenerate

rendelni out = Fu [3] .o_q;

endmodule

nyelvi konstrukció generál-endgenerate lehetővé teszi, hogy állítsa be a kívánt példányszámot funkcionális modul és csatlakoztassa őket egymással, ha szükséges. Ezen kívül minden példányát funkcionális modul is paraméterezhető, hogy „tudjuk helyükön”: ebben a példában # (index) - azt át paramétermodulból helyzetben modul viselkedését függhet ezt a paramétert. A fenti példa teszi éppen egy ilyen rendszer:

Ez a ciklus is létrehozhat, például a szerkezet 1000 csatlakoztatott modulok. Hogyan kell felhívni, hogy ez a kör? Meddig fog tartani? És hirtelen húztam egy diagramot, majd meg kell adni a jelet a modul, hogy minden újra megjavít dolgozza át? Ez nehéz lesz.

Ott van még a érv a grafikus fájlokat - láthatóságát. Man állítólag jelenlegi rendszer és végrehajtására, mert egy ötlet könnyebb ütemezni. Mi van azzal érvelni? Gondolom egy ilyen rendszer, de én azonnal leírni a Verilogban. Valójában úgy gondolom, hogy az a személy, aki azt írja, a Verilog / VHDL azonnal bemutatni magát a fej áramkör a szövegben leírt - ez jobb és amilyennek lennie kellene.

Sajnos azt kell mondanom, hogy én személy szerint nagyon gyakran van egy probléma olvasás rendszereket. Íme egy példa.

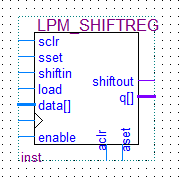

Látom a rendszerben kell LPM_SHIFTREG szabványos eleme a grafikus könyvtár Altera Quartus II. Kihez csak azt, amit jel nagyobb prioritású, sclr vagy terhelést. Mi történik, ha mindketten aktív lesz? Meg lehet írva a nyilvántartást minden nulla, vagy fogja tölteni az új adatokat a léptető regiszterbe? Tehát mindig elfelejtem. Nézem ezt a komponenst az áramkörben, és nem emlékszem, hogy mit jelent ez az egész. Azt hiszem, van egy kis tapasztalat rendszerek ..

A verilogom könnyebb. Nem allegorikus:

reg [7: 0] serial_send_reg;

Mindig @ (posedge clk)

if (sclr)

serial_send_reg <= 0;

más

if (terhelés)

serial_send_reg <= next_data;

más

serial_send_reg <=

A leírás Verilog HDL jelzi prioritások azonnal láthatók a szövegben.

Általában több vizuális reprezentációja a projekt én személyesen nem részesíti előnyben rendszereket.

Hordozhatóság és a hordozhatóság a projektek.

Azt hiszem, ez világos. Ha egy fejlesztő akarja fejleszteni is lehetne használni, máshol, kivéve annak FPGA, akkor kell használni, hogy szöveges leírások Verilog / VHDL. Ez csak azért történik, hogy nincs egységes szabvány leírja a grafikus fájlok, digitális áramkörök ma. Kiderült, hogy az Altera képfájl formátumban, míg Xilinx saját. És gyártói ASIC chipek nem fog grafikai tervezés, lesz munkája csak szöveget.

Mi a mi fórumon Marsohod2 Amber nyílások a nyílt forráskódú projekt opencores - ez volt eredetileg a Xilinx chipset nyelvén Verilog HDL. Most már tudjuk, hogy elkészítse FPGA Altera Cyclone III. Ha lenne egy tervezet formájában diagramok, azt hiszem, nem lenne esélye.

Általában vizualizációs rendszerek - ez az egész probléma. Ha meg kell mutatni a projekt a rendszer néhány szakértő, az első dolog, amit meg kell tennie - meg magad egy fejlesztői környezet, és indítsa el a szivattyú az interneten telepítőcsomag mérete 3-4 GB. És ez nem fut-e vagy sem, ha a személy nem érdemes nagyon elterjedt operációs rendszer a számítógépen. És ha én vagyok az úton, és nem volt vele csak egy iPad vagy Galaxy Tab? A szöveg még mindig lehet látni, de a rendszer bonyolult.

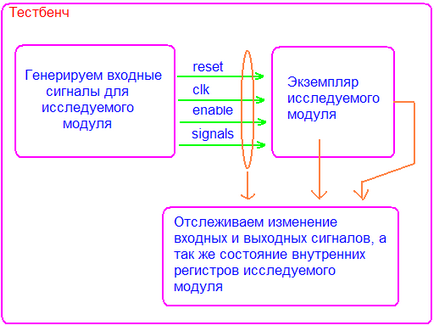

Fontos eleme a fejlesztési folyamat a digitális áramkörök - azonosítást. Egyszerűen fogalmazva - ez modellezése a projekt vagy a modulok. Abban az esetben, szöveg projektek tesztelési folyamat a következő: egy külön programot írt-testbench. testbench program írt ugyanazon a nyelven, mint a projekt maga. Például a projekt célja a Verilogban. Testbench is elvégezhető a Verilogban.

testbencha program megvizsgálja a kész modul, mint egy fekete doboz, az összes bemenő jelet a fekete doboz szimulálja, a kimenetek a vizsgálati egység látjuk és azt látták, hogy rendeltetésszerűen. Mi a program hatása a teszt modult és ellenőrzi a választ. Sok eszköz az ilyen ellenőrzést. Company Altera szállít annak ModelSim Altera Quartus II tervezési környezet környezet - csak szimulálni Verilog / VHDL tervez. Van egy nyílt forráskódú projekt Icarus Verilog funkcionális szimulációs projektek. ÉN használ ez igen gyakran - nagyon egyszerű eszköz.

Érdekes, hogy sok gyártó biztosítja chip Verilog modell a zseton, hogy a fejlesztők egyszerűbben debug projekteket.

Számos jó példa a szimulációs projektek honlapunkon. Például szimuláljuk a rendszer az Amber chip és fut a Linux operációs rendszer a rendszerben. Ez egy nagyon bonyolult a szimuláció, hogy tartalmazza a modell SDRAM memóriát, a nagyon system-on-chip a processzor, a bootrom, soros port, időzítő, megszakítás vezérlő. A szimuláció során a elemezte a processzor végrehajt millió utasításokat. Nyilvánvaló, hogy egy ilyen hosszú távú szimulációt lefedi gyakorlatilag az összes lehetséges belső állapotok a rendszer. Azt reméljük, hogy a projekt megfelelően működik.

A telephelyünkön még egyszer felülvizsgálja a szimulátorban Quartus II v9. Ez volt régen. A későbbi verziói Altera tervezési környezet szimulátor kizárták a csomagot. Nos az igazság az, nem volt túl jó.

Mi a teendő most? Csak egy módja annak, hogy szimulálják áramkör kvartusa környezetben. Nyissa meg a sémafájl majd a Fájl menü => Create / Update => Create HDL tervezése Fájl Current File. Ennek eredményeként a rendszer átalakul egy szöveges fájlt a nyelv a Verilog vagy VHDL. Nos, akkor, mint minden más ember - használja ModelSim.

Nem kényelmes, van még egy közbenső szakaszában az átalakítás. Ha több helyes séma és átalakítani, hogy a szimuláció, akkor még lesz egy gyötrelem.

Gyakran előfordul, hogy néhány szükséges funkciót egyszer dolgozott, majd hirtelen megállt. Miért? Miért? Mikor és ki korrigálta a projektben? Hogyan változások nyomon követése a projekt időben?

A szoftver projektek a C / C ++, C #, PHP, Python, és az összes többi fenntartani a projekt az a tároló szerver. Egy tipikus példa a forrás-ellenőrző rendszer - ez a rendszer Subversion vagy GIT. Ezek a rendszerek lehetővé teszik, hogy módosítsa a tervezetet kódot, és mentse köztes állapotok a projekt. Lehetőség van arra is, hogy ágaznak a projekt, a projekt munka egyesíteni az ágak a fő áramlási a projekt, és így tovább. Talán valamikor meg kell találni, hogy ki és mikor és miért, hogy néhány változtatást, akkor vissza kell állítani egy korábbi változata a projekt. Csak a használata verziókövető rendszerek lehetővé teszi, hogy egy nagy projekt van.

Mindez természetesen vonatkozik a szöveges leírások a hardver projektek Verilog / VHDL.

Példa a projektek egy verziókezelő rendszer - Amber-Marsohod2 - számhordozás rendszer az opensource Amber pristalle kártya Marsohod2. Az egész folyamat a számhordozás a nyilvánosság GitHubról. És ez jó.

Ha használja a szöveges fájlokat nagyon könnyű összehasonlítani a különböző változatai azonos modult. Akkor egyszerűen konzol diff parancs Linux alatt. Vagy van egy eszköz összehasonlítása és egyesítése szöveges fájlok meld típusát.

De mondja meg, hogyan kell összehasonlítani a két rendszer: egy kicsit idősebb, és egy kicsit több, mint egy újat? Nem tudom. Hiánya miatt az eszközök összehasonlításának grafikus rendszer használ VCS lesz nagyon problematikus, és kényelmetlen. Itt egy másik, és jelentős ellenérv rendszereket.

Következtetés tudom csinálni. Egy szöveges leírására a hardver projektek sok esetben előnyös. A fényképek beviteli eszköz lehet egyszer és jöjjön vissza, de csak akkor, ha nem lesz szabványok tárolási rendszereket és eszközöket, amelyek megkönnyítik a bemeneti áramkörök ellenőrzési és összehasonlítások.