Az órajel-generátor

Az órajel-generátor áll egy aluláteresztő RC-oszcillátor, a fő óra és PLL egység (PLL). Itt készülnek a következő időjeleik:

- SLCK, alacsony frekvenciájú órajelet, a rendszeren belül

- MAINCK így fő órajel generátor

- PLLCK kiadási PLL modul és frekvenciaosztó

Interface órajel generátor van beépítve az energiafogyasztás vezérlő PMC és fejezetben ismertetjük 26.9. Azonban az óra regisztrálja a nevét kombináljuk CKGR_ csoportban.

25.2 Alacsony frekvencia RC oszcillátor

Az alacsony frekvenciájú RC oszcillátor - az egyetlen állandó órajelet a rendszeren belül, beleértve az áramfogyasztás vezérlő PMC. Ez szükséges jel a PMC. A felhasználónak meg kell venniük a lehetséges elsodródás RC oszcillátor. További részletes információkat kap a jellemzők részén DC.

25.3 mester órajel

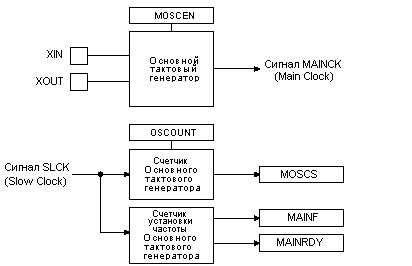

A ris.25-1 tömbvázlatát mutatja az órajel-generátor.

Ábra. 25-1. Strukturális órajel generátor áramkört

25.3.1 engedélyezése fő órajel generátor

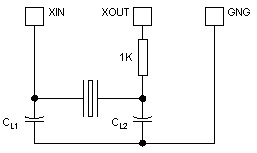

A órajel-generátor tartalmaz egy fő órajel oszcillátor működő kristály gyakorisága 3 és 20 MHz. Tipikus kapcsolási rajz mutatja ris.25-2 kvarc. Amikor dolgozik kvarc frekvencián akár 8 MHz igényel beállítást ellenállás 1K. Terminálo- Xin és XOUT csatlakozik kondenzátorok 25 pF. Következésképpen, CL1 és CL2 tartály elhagyható, alkalmazásával kvarc egyenlő bemeneti kapacitás 12,5 pF. További részletes információkat az elektromos jellemzők megadott jellemzőkkel részén DC.

Ábra. 25-2. Egy tipikus áramkörét kvarcrezonátor

25.3.2 kezdési időpont fő órajel generátor

indítsa el a fő óra időt egy adott szakaszon a DC jellemzőit. futási idő függ a kvarc gyakorisága és csökken a frekvencia növekedésével.

25.3.3 Ellenőrző alap órajel

Csökkenni induláskor energiafogyasztás a fő órajel le van tiltva, és az alacsony frekvenciájú RC oszcillátor van kiválasztva.

Szoftver engedélyezni / letiltani a fő órát, hogy csökkentse az energiafogyasztást. Ez úgy történik, hogy visszaállítjuk MOSCEN kicsit a nyilvántartásban a fő generátor (CKGR_MOR).

Leválasztása a fő óra visszaállítása kicsit MOSCEN CKGR_MOR vezet automatikus visszaállítás MOSCS PMC_SR kicsit a nyilvántartásban, jelezve, hogy az elsődleges óra van tiltva.

Ha a felbontás a fő generátor, a felhasználónak kell inicializálni a számláló értékét a fő generátorok, a megfelelő kezdési időpont a generátort. Kezdés ideje gyakoriságától függ a csatlakoztatott kvarc.

A felvétel után MOSCEN OSCOUNT bitek és értékek a nyilvántartásban, hogy lehetővé tegye CKGR_MOR főgenerátor, MOSCS kicsit a status terül PMC_SR állítani. A számláló akkor kezdi a mérést az érték a csökkenés OSCOUNT gyakorisággal jel frekvencia 8-szor SLCK jelet. Mivel OSCOUNT érték kódolva 8 bit, akkor a maximális indítási idő mintegy 62 ms.

Amikor a számláló eléri a nullát, MOSCS van beállítva, ami azt jelzi, hogy a fő oszcillátor frekvencia létre. Beállítása egy kicsit MOSCS PMC_IMR lehet egy élet forrása a megszakítást a processzor.

25.3.4 szerelvény fő oszcillátor frekvencia számláló

Counter frekvencia beállítás főgenerátor pontosan meg tudja határozni a frekvencia a kristály oszcillátor csatlakozik. Ez hasznos lehet egy programot rakodó palackok mikrokontroller konfiguráció megfelelő értéket az órajel, függetlenül az alkalmazás.

Counter fő oszcillátor frekvencia beállítása kezd számolni a mester órajel generátor sebességét után előfordulása pozitív él az alacsony frekvenciájú oszcillátor (SLCK jel) után a stabilizációs a fő órajel, azaz, ha telepítve MOSCS bit. Aztán a 16. lefutó él jel SLCK MAINRDY bit be van állítva a nyilvántartásba fő óra CKGR_MCFR (Main Clock Frequency Register) és számláló leáll a gróf. Ez az érték olvasható a regisztrációhoz MAINF CKGR_MCFR és megegyezik a ciklusok száma az alapvető ütemadó 16 időszakokra SLCK jelet. Így, a frekvencia a kvarcrezonátor csatlakoztatva lehet meghatározni.

25.3.5 Külső oszcillátor

külső órajel is csatlakoztatható helyett csatlakozik a vezérlő kvarc. Ebben az esetben a külső órajel jut a terminál Xin. XIN bemeneti kimeneti karakterisztikája ilyen körülmények között mutatjuk be a részében, az elektromos jellemzők. A programozó nem szabad elfelejteni OSCBYPASS bit 1-be, és MOSCEN bit 0 a nyilvántartásban főgenerátor CKGR_MOR (Main OSC Register) megfelelő működését egy külső órajelet.

25,4 PLL és frekvenciaosztó

PLL szerepel a bemeneti osztó pontosságának növelése céljából a kapott órajelet. Azonban a felhasználónak ki kell választani egy minimális értéke a frekvencia PLL bemeneti osztó programozás során.

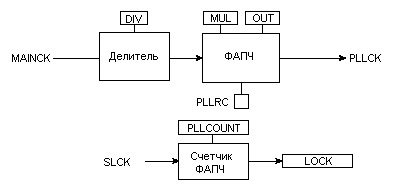

On ris.25-3. ábra tömbvázlata egy PLL és frekvenciaosztó.

Ábra. 25-3. A blokk diagram a PLL és frekvenciaosztó

25.4.1 Szűrés PLL

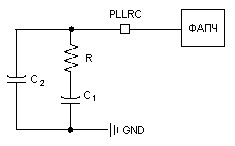

PLL internetkapcsolatot igényel külső szűrő rend 2 porton keresztül PLLRC. On ris.25-4 mutatja egy ilyen szűrő áramkör.

Ábra. 25-4. Vonatkozó rendszer PLL szűrő

Névleges értékek R, C1 és C2, csatlakozik a következtetésre PLLRC, függvényében számított a bemeneti frekvencia a PLL, a PLL kimeneti frekvencia és fázis. Válogatás az optimális értékek végzi a sebességváltó kimenő jelet, és a kezdés időpontját.

25.4.2 programozása PLL és frekvenciaosztó

Az elválasztó lehet beállítani a 1-től 255-ig felvételkészítés közben az elválasztó DIV nulla a kimenetek a megfelelő elválasztó és PLL beállítása alacsony szintű jelet. Újraindítás után, minden területen van rögzítve DIV nulla, ami a nullázó a megfelelő órajel bemenet a PLL.

PLL segítségével szorzás jel kimenet a elválasztó. A frekvencia a PLL órajel frekvenciájától függ az eredeti jel és paraméterek DIV és MUL. Az érték a kimenő frekvencia határozza meg expressziót (MUL + 1) / DIV. Írás a MUL nulla letiltja a PLL. Felvétele a PLL áramkör a felvétel MUL értéke nagyobb, mint nulla.

A bekapcsolás után a PLL vagy megváltoztathatja annak egyik paraméter LOCK bit a nyilvántartásban automatikusan kikapcsol PMC_SR. A feljegyzett értékek PLLCOUNT területén CKGR_PLLR regiszter betöltődnek a PLL számláló. Counter PLL majd csökkentjük a sebesség jelet SLCK eléri a nullát. Ezen a ponton PMC_SR LOCK bit a nyilvántartásba be van állítva, és generál egy megszakítást a processzor. A felhasználónak kell letölteni SLCK számú jel ciklusok PLLCOUNT területen, amely meghatározza az átfedés az átalakulási folyamat a PLL. Az időtartam a tranziens folyamat függ a PLL szűrőn. A kezdeti paraméterek és a PLL kimeneti frekvencia lehet kiszámítani egy speciális eszköz segítségével, amely Atmel.